# Dynamic power-aware techniques for real-time multicore embedded systems

**JOSÉ LUIS MARCH CABRELLES**

### Universitat Politècnica de València

#### Ph.D. Thesis

# Dynamic Power-Aware Techniques for Real-Time Multicore Embedded Systems

Author: Advisors:

José Luis March Cabrelles Prof. Salvador V. Petit Martí

Prof. Julio Sahuquillo Borrás

A thesis submitted in partial fulfillment of the requirements for the degree of

> Doctor of Philosophy (Computer Engineering)

> > in the

Parallel Architectures Group

Department of Computer Engineering

December 2014

#### **Collection Doctoral Thesis**

© José Luis March Cabrelles

© 2015, of the present edition: Editorial Universitat Politècnica de València Telf.: 963 877 012 / www.lalibreria.upv.es

ISBN: 978-84-9048-327-5 (printed version)

Any unauthorized copying, distribution, marketing, editing, and in general any other exploitation, for whatever reason, of this piece of work or any part thereof, is strictly prohibited without the authors' expressed and written permission.

This guy's walking down a street when he falls in a hole. The walls are so steep, he can't get out. A doctor passes by, and the guy shouts up, "Hey you, can you help me out?" The doctor writes a prescription, throws it down in the hole and moves on. Then a priest comes along, and the guy shouts up "Father, I'm down in this hole, can you help me out?" The priest writes out a prayer, throws it down in the hole and moves on. Then a friend walks by. "Hey Joe, it's me, can you help me out?" And the friend jumps in the hole. Our guy says, "Are you stupid? Now we're both down here." The friend says, "Yeah, but I've been down here before, and I know the way out."

Leo McGarry (played by John Spencer), The West Wing.

#### TECHNICAL UNIVERSITY OF VALENCIA

### Abstract

School of Computer Engineering

Department of Computer Engineering

Doctor of Philosophy (Computer Engineering)

#### Dynamic Power-Aware Techniques for Real-Time Multicore Embedded Systems

by José Luis March Cabrelles

The continuous shrink of transistor sizes has allowed more complex and powerful devices to be implemented in the same area, which provides new capabilities and functionalities. However, this complexity increase comes with a considerable rise in power consumption. This situation is critical in portable devices where the energy budget is limited and, hence, battery lifetime defines the usefulness of the system. Therefore, power consumption has become a major concern in the design of real-time multicore embedded systems.

This dissertation proposes several techniques aimed to save energy without sacrifying real-time schedulability in this type of systems. The proposed techniques deal with different main components of the system. In particular, the techniques affect the task partitioner and the scheduler, as well as the memory controller.

Some of the techniques are especially tailored for multicores with shared *Dynamic Voltage and Frequency Scaling* (DVFS) domains. Workload balancing among cores in a given domain has a strong impact on power consumption, since all the cores sharing a DVFS domain must run at the speed required by the most loaded core.

In this thesis, a novel **workload partitioning** algorithm is proposed, namely *Load-bounded Resource Balancing* (*LRB*). The proposal allocates tasks to cores to balance a given resource (processor or memory) consumption among cores, improving real-time schedulability by increasing overlapping between processor and memory. However, distributing tasks in this way regardless the individual core utilizations could lead to unfair load distributions. That is, one of the cores could become much loaded than the others. To avoid this scenario, when a given utilization threshold is exceeded, tasks are assigned to the least loaded core.

vi

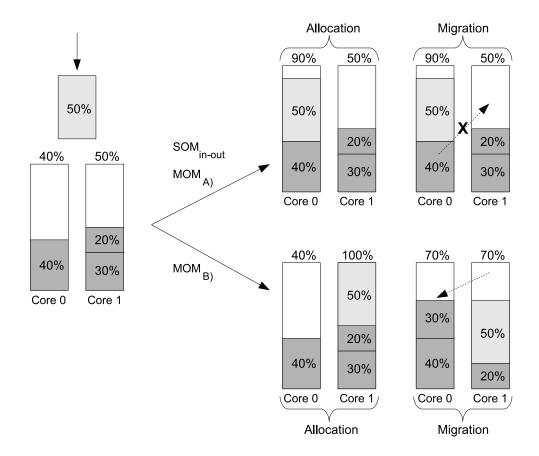

Unfortunately, workload partitioning alone is sometimes not able to achieve a good workload balance among cores. Therefore, this work also explores novel **task migration** approaches. Two task migration heuristics are proposed. The first heuristic, referred to as Single Option Migration (SOM), attempts to perform only one migration when the workload changes to improve utilization balance. Three variants of the SOM algorithm have been devised, depending on the point of time the migration attempt is performed: when a task arrives to the system  $(SOM_{in})$ , when a task leaves the system  $(SOM_{out})$ , and in both cases  $(SOM_{in-out})$ . The second heuristic, referred to as Multiple Option Migration (MOM) explores an additional alternative workload partitioning before performing the migration attempt.

Regarding the memory controller, **memory controller scheduling policies** are devised. Conventional policies used in *Non Real-Time* (NRT) systems are not appropriate for systems providing support for both *Hard Real-Time* (HRT) and *Soft Real-Time* (SRT) tasks. Those policies can introduce variability in the latencies of the memory requests and, hence, cause an HRT deadline miss that could lead to a critical failure of the real-time system. To deal with this drawback, a simple policy, referred to as *HR-first*, which prioritizes requests of HRT tasks, is proposed. In addition, a more advanced approach, namely *ATR-first*, is presented. *ATR-first* prioritizes only those requests of HRT tasks that are necessary to ensure real-time schedulability, improving the *Quality of Service* (QoS) of SRT tasks.

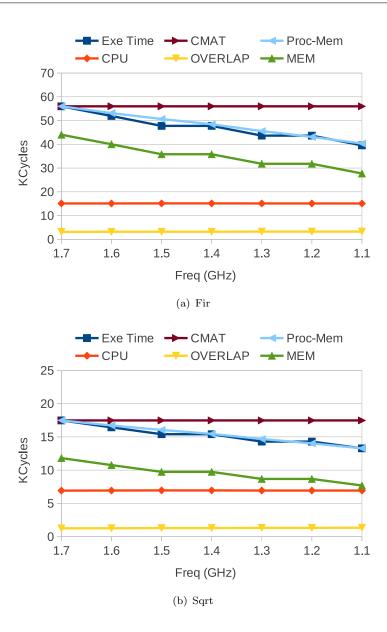

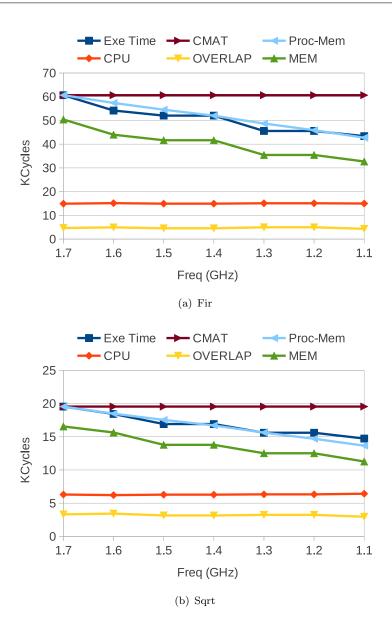

Finally, this thesis also tackles **dynamic execution time estimation**. The accuracy of this estimation is important to avoid deadline misses of HRT tasks but also to increase QoS in SRT systems. Besides, it can also help to improve the schedulability of the systems and reduce power consumption. The *Processor-Memory (Proc-Mem)* model, that dynamically predicts the execution time of real-time application for each frequency level, is proposed. This model measures at the first hyperperiod, making use of *Performance Monitoring Counters* (PMCs) at run-time, the portion of time that each core is performing computation (*CPU*), waiting for memory (*MEM*), or both (*OVERLAP*). This information will be used to estimate the execution time at any other working frequency.

#### UNIVERSIDAD POLITÉCNICA DE VALENCIA

### Resumen

Escuela Técnica Superior de Ingeniería Informática Departamento de Informática de Sistemas y Computadores

> Doctor en Filosofía (Ingeniería Informática)

Técnicas Dinámicas con Control de Consumo para Sistemas Empotrados Multinúcleo de Tiempo Real

por José Luis March Cabrelles

La continua reducción del tamaño de transistor ha permitido la implementación de dispositivos más complejos y potentes en una misma área, lo que proporciona una mayor capacidad y funcionalidad. Sin embargo, este incremento en la complejidad conlleva un considerable aumento del consumo energético. Esta situación es crítica en dispositivos móviles, donde la capacidad energética está limitada y, por lo tanto, la vida útil de la batería define la usabilidad del sistema. En consecuencia, el consumo energético se ha convertido en un aspecto crucial en el diseño de sistemas empotrados multinúcleo de tiempo real.

Esta disertación propone diversas técnicas con el objetivo de ahorrar energía sin sacrificar la planificabilidad de tiempo real en este tipo de sistemas. Las técnicas propuestas actúan sobre diferentes componentes principales del sistema. En particular, estas técnicas afectan al particionador de tareas y al planificador, así como al controlador de memoria.

Algunas de estas técnicas están especialmente concebidas para sistemas multinúcleo con dominios DVFS (*Dynamic Voltage and Frequency Scaling*) compartidos. Equilibrar la carga entre los núcleos en un dominio dado tiene un fuerte impacto en el consumo de energía, ya que todos los núcleos que comparten un dominio DVFS deben funcionar a la velocidad requerida por el núcleo más cargado.

En esta tesis se propone un nuevo algoritmo de **particionado de carga**, denominado Load-bounded  $Resource\ Balancing\ (LRB)$ . La propuesta asigna las tareas a los núcleos para equilibrar el consumo de un recurso dado (procesador o memoria) entre los núcleos, mejorando la planificabilidad de tiempo real al incrementar el solapamiento entre procesador y memoria. Sin embargo, distribuir las tareas de esta forma sin tener en cuenta

viii Resumen

la utilización individual de los núcleos podría dar lugar a distribuciones de carga desequilibradas. Es decir, uno de los núcleos podría estar mucho más cargado que el resto. Con tal de evitar este escenario, cuando se supera un umbral de utilización dado, las tareas son asignadas al núcleo menos cargado.

Desafortunadamente, sólo con el particionado de carga a veces no es suficiente para conseguir un buen equilibrado de carga entre los núcleos. Por lo tanto, este trabajo también explora nuevas aproximaciones basadas en **migración de tareas**. Se proponen dos heurísticas con migración de tareas. La primera heurística, llamada Single Option Migration (SOM), intenta realizar sólo una migración cuando la carga cambia para mejorar el equilibrio de la utilización. Se han ideado tres variantes del algoritmo SOM, en función del instante de tiempo en el que se realiza el intento de migración: cuando una tarea llega al sistema ( $SOM_{in}$ ), cuando una tarea sale del sistema ( $SOM_{out}$ ), y en ambos casos ( $SOM_{in-out}$ ). La segunda heurística, denominada Multiple Option Migration (MOM), explora un particionado de carga alternativo adicional antes de realizar el intento de migración.

Respecto al controlador de memoria, se han concebido dos **políticas de planificación para el controlador de memoria**. Las políticas convencionales usadas en sistemas que no son de tiempo real no son apropiadas para sistemas que dan soporte a tareas tanto de tiempo real estricto (*Hard Real-Time* o HRT) como de tiempo real flexible (*Soft Real-Time* o SRT). Esas políticas pueden introducir variabilidad en las latencias de las peticiones de memoria y, por consiguiente, causar una pérdida de deadlines que podría conllevar un fallo crítico del sistema de tiempo real. Para tratar este inconveniente, se propone una política simple, denominada *HR-first*, que prioriza peticiones de tareas HRT. Además, se presenta una aproximación más elaborada, llamada *ATR-first*. *ATR-first* prioriza sólo aquellas tareas HRT que son necesarias para asegurar la planificabilidad de tiempo real, mejorando la calidad de servicio (*Quality of Service* o QoS) de las tareas SRT.

Finalmente, esta tesis también aborda la **estimación dinámica del tiempo de ejecución**. La precisión de esta estimación es importante para evitar la pérdida de deadlines de tareas HRT, pero también para incrementar la QoS en sistemas SRT. Además, también puede ayudar a mejorar la planificabilidad del sistema y reducir el consumo de energía. Se propone el modelo *Processor-Memory* (*Proc-Mem*), que dinámicamente predice el tiempo de ejecución de aplicaciones de tiempo real para cada nivel de frecuencia. Este modelo mide en el primer hiperperiodo, haciendo uso de *Performance Monitoring Counters* (PMCs) en tiempo de ejecución, la porción de tiempo que cada núcleo está realizando cómputos (*CPU*), esperando a memoria (*MEM*), o ambos (*OVERLAP*). Esta información será usada para estimar el tiempo de ejecución a cualquier otra frecuencia.

#### UNIVERSITAT POLITÈCNICA DE VALÈNCIA

### Resum

Escola Tècnica Superior d'Enginyeria Informàtica Departament d'Informàtica de Sistemes i Computadors

> Doctor en Filosofia (Enginyeria Informàtica)

#### Tècniques Dinàmiques amb Control de Consum per a Sistemes Encastats Multinucli de Temps Real

per José Luis March Cabrelles

La contínua reducció de la grandària dels transistors ha permès la implementació de dispositius més complexes i potents en una mateixa àrea, proporcionant una major capacitat i funcionalitat. No obstant, aquest increment en la complexitat comporta un considerable augment del consum energètic. Aquesta situació és crítica en dispositius mòbils, on la capacitat energètica està limitada i, per tant, la vida útil de la bateria defineix la usabilitat del sistema. En conseqüència, el consum energètic s'ha convertit en un aspecte crucial en el disseny de sistemes encastats multinucli de temps real.

Aquesta dissertació proposa diverses tècniques amb l'objectiu d'estalviar energia sense sacrificar la planificabilitat de temps real en aquest tipus de sistemes. Les tècniques proposades actuen sobre diferents components principals del sistema. En particular, aquestes tècniques afecten el particionador de tasques i el planificador, així com el controlador de memòria.

Algunes d'aquestes tècniques estan especialment concebudes per a sistemes multinucli amb dominis DVFS (*Dynamic Voltage and Frequency Scaling*) compartits. Equilibrar la càrrega entre els nuclis en un domini donat té un fort impacte en el consum d'energia, ja que tots els nuclis que comparteixen un domini DVFS han de funcionar a la velocitat requerida pel nucli més carregat.

En aquesta tesi es proposa un nou algorisme de **particionat de càrrega**, anomenat Load-bounded Resource Balancing (LRB). La proposta assigna les tasques als nuclis per equilibrar el consum d'un recurs donat (processador o memòria) entre els nuclis, millorant la planificabilitat de temps real en incrementar el solapament entre processador i memòria. No obstant, distribuir les tasques d'aquesta manera sense tenir en compte la

x Resum

utilització individual dels nuclis podria donar lloc a distribucions de càrrega desequilibrades. És a dir, un dels nuclis podria estar molt més carregat que la resta. Per tal d'evitar aquest escenari, quan se supera un llindar d'utilització donat, les tasques són assignades al nucli menys carregat.

Desafortunadament, només amb el particionat de càrrega de vegades no és suficient per aconseguir un bon equilibrat de càrrega entre els nuclis. Per tant, aquest treball també explora noves aproximacions basades en **migració de tasques**. Es proposen dues heurstiques amb migració de tasques. La primera heurística, anomenada Single Option Migration (SOM), intenta realitzar només una migració quan la càrrega canvia per millorar l'equilibri de la utilització. S'han ideat tres variants de l'algorisme SOM, en funció de l'instant de temps en què es realitza l'intent de migració: quan una tasca arriba al sistema ( $SOM_{in}$ ), quan una tasca surt del sistema ( $SOM_{out}$ ), i en ambdós casos ( $SOM_{in-out}$ ). La segona heurística, anomenada Multiple Option Migration (MOM), explora un particionat de càrrega alternatiu addicional abans de fer l'intent de migració.

Respecte al controlador de memòria, s'han concebut dos **polítiques de planificació per al controlador de memòria**. Les poltiques convencionals usades en sistemes que no són de temps real no són apropiades per a sistemes que donen suport a tasques tant de temps real estricte (*Hard Real-Time* o HRT) com de temps real flexible (*Soft Real-Time* o SRT). Aquestes polítiques poden introduir variabilitat en les latències de les peticions de memòria i, per tant, causar una pèrdua de deadlines que podria comportar una fallada crítica del sistema de temps real. Per tractar aquest inconvenient, es proposa una política simple, anomenada *HR-first*, que prioritza peticions de tasques HRT. A més, es presenta una aproximació més elaborada, anomenada *ATR-first*. *ATR-first* prioritza només aquelles tasques HRT que són necessàries per a assegurar la planificabilitat de temps real, millorant la qualitat de servei (*Quality of Service* o QoS) de les tasques SRT.

Finalment, aquesta tesi també aborda la estimació dinàmica del temps d'execució. La precisió d'aquesta estimació és important per evitar la pèrdua de deadlines de tasques HRT, però també per incrementar la QoS en sistemes SRT. A més, també pot ajudar a millorar la planificabilidad del sistema i reduir el consum d'energia. Es proposa el model Processor-Memory (Proc-Mem), que dinàmicament prediu el temps d'execució d'aplicacions de temps real per a cada nivell de freqüència. Aquest model mesura en el primer hiperperíode, fent ús de Performance Monitoring Counters (PMCs) en temps d'execució, la porció de temps que cada nucli està realitzant còmputs (CPU), esperant a memòria (MEM), o ambdós (OVERLAP). Aquesta informació serà usada per estimar el temps d'execució a qualsevol altra freqüència.

### Acknowledgements

This work would have never been possible without the support of many people throughout these years. First of all, I have to mention my parents and my sister, without whom I would not be who I am. Second, I also have to acknowledge my advisors Salva Petit and Julio Sahuquillo, as well as Houcine Hassan, for their guidance and help in achieving this goal.

Looking back, I started my journey in this university ten years ago. Now, after an Engineering Degree, a Master's Degree and a Ph.D., I am happy to remember a lot of moments and experiences, and so I want to thank everyone in the university that helped me feel really comfortable all these years. *Thanks*.

Regarding my research group mates, I appreciate the great atmosphere they all have built, not only at work but also going out together for lunch or dinner, japanese food, paella or torrà at Carlos' place, karting, etc. Although the full list would be longer, I would like to mention Roberto, Crispín, Carlos, Josué, José María, Davide, Javi, José Cano, etc. Moreover, working in my laboratory allowed me to build up a good friendship with Raúl and Mónica. I had interesting and deep discussions with them about everything including, of course, food and running. The three of us became an excellent team facing the daily problems of work and life. Finally, a special mention deserve both biondi Alejandro Valero and Mario Lodde, with whom I shared a lot of conversations, laughs, travels, concerts, conferences and, in the end, great moments. I met Mario when studying our Master's Degree, he taught me italian and music stuff and, as years went by, we were turning into closer amici. Alex and I became so good friends that we even shared an apartment (with a Death Room and a Rat's Room) for almost two years of our lives. Currently, we are far away from each other due to our jobs, however, I know with them I have two trusty friends no matter where we are. Grazie Mille a Tutti.

I would like to thank Blas for introducing me to Fútbol Xtreme, where I have not only enjoyed playing football but I have also made a lot of friends. As I have been able to confirm throughout my life (C.I.L., C.D. Deportes Arnau, C.D. Serranos, Fac-In, Los de Siempre, Alfonso, HideSport, Nottingham Por, etc.), that is the main result of playing football: to make friends. In fact, I have to acknowledge football itself, as well as running, music, movies and TV series, for being such a useful tool to face stress periods during the development of this work. Gracias.

From my stay at the MDH (Mälardalens Högskola) in Västerås (Sweden), I am very grateful to Thomas Nolte and Moris Behnam. They were very kind, introducing me to

their research group and making me feel like anyone else on the team. By the way, an excellent group of people not only in research duties but also in a personal sense. In the same way, several nice words should be said about some friends I made in Västerås. Sama and Richi were gentle and helpful in the time we spent together. Miguel and Laura are my family in Sweden, and I know I can count on them. And with Berta I had deep and enriching discussions about life and muffins. Tack Så Mycket.

Here in Spain I also had friends that supported me during all these years: Roman, Caraltu, Cenci, Maci, Toni, Kent, Amparo, Yasmin, Paula, Cedric, etc. I remember with special affection the year I shared an apartment with Francesco and Silvia. More recently, last year I shared another apartment with Jaume and Dani, and they quickly turned from flatmates into actual friends. Back to the past again, I met Irene fifteen years ago at school, and despite we now live in different cities, she is always there to state a helpful judgement in anything that happens in my life. Gràcies.

Crossing the Atlantic Ocean until Brazil, I can not forget Dra. Dra. Juliana Dos Anjos, who was a really close friend during her stay in Valencia. If we go further through the Pacific Ocean we will arrive in Japan and find Dr. Pablo Lamilla (a.k.a. Buci). He was a constant support when we were at university in Valencia studying together and also later when he moved to Kōchi. *Muito Obrigado & Dōmo Arigatō*.

And last but not least, I really would like to thank my most true friends Alejandro Arcos and Jonatan Linares (a.k.a. Xona). Arcos is always there to contradict me, even when he agrees with me. We shared many moments, at university, in the football field or traveling. And he hosted me many times in London and Madrid, where I felt like home. With Xona I also shared many experiences, working together in university projects, talking about movies and soundtracks, having lunch at Tony's or driving a Jeep through the caribbean jungle. Besides, he is a dynamic entrepreneurial endeavour with many start-up projects in his mind, in which I try to help him. The three of us shared many great nights, starting with bravas at La Rosa Negra having deep discussions and laughs, and ending where the flow takes us. I know Arcos and Xona for ten years, and they were always with me in the good, the bad and the ugly times.

# Contents

| Ab  | ract                                                                                                                                                             | v                               |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Res | rmen v                                                                                                                                                           | ii                              |

| Res | ım i                                                                                                                                                             | x                               |

| Acl | nowledgements                                                                                                                                                    | κi                              |

| Co  | zents xi                                                                                                                                                         | ii                              |

| Lis | of Figures xv                                                                                                                                                    | ii                              |

| Lis | of Tables xi                                                                                                                                                     | x                               |

| Acı | onyms xx                                                                                                                                                         | ۲i                              |

|     |                                                                                                                                                                  | 1<br>1<br>2<br>3<br>4<br>4<br>7 |

| :   | 1 Real-Time Scheduling in Power-Aware Multicore Processors                                                                                                       | 9<br>11<br>12<br>13             |

| ;   | 1 Baseline Design       1         3.1.1 Real-Time Tasks       1         3.1.2 Power-Aware Scheduler       1         2 The Multi2Sim Simulation Framework       2 | .7<br>17<br>19<br>19            |

xiv Contents

|   |     | 3.2.2 Main Proposed Extensions                                   |   |   | <br>. 22       |

|---|-----|------------------------------------------------------------------|---|---|----------------|

|   |     | 3.2.2.1 Task Repetition                                          |   |   | <br>23         |

|   |     | 3.2.2.2 Priority                                                 |   |   | <br>24         |

|   |     | 3.2.2.3 Frequency                                                |   |   | <br>25         |

|   |     | 3.2.2.4 Latency of Frequency Changes                             |   |   | <br>25         |

|   |     | 3.2.2.5 Task Partitioner                                         |   |   | <br>26         |

| 4 | Tas | k Partitioning                                                   |   |   | 29             |

|   | 4.1 | Introduction                                                     |   |   | <br>29         |

|   | 4.2 | Partitioning Heuristics                                          |   |   | <br>30         |

|   |     | 4.2.1 HRT Heuristic                                              |   |   | <br>30         |

|   |     | 4.2.2 Power-Aware HRT Scheduler                                  |   |   | <br>31         |

|   |     | 4.2.3 Providing Support for SRT Tasks                            |   |   | <br>32         |

|   | 4.3 | Experimental Evaluation                                          |   |   | <br>35         |

|   |     | 4.3.1 Designing and Planning Mix Execution for HRT Tasks         |   |   | <br>36         |

|   |     | 4.3.2 Designing Hybrid Mixes                                     |   |   | <br>39         |

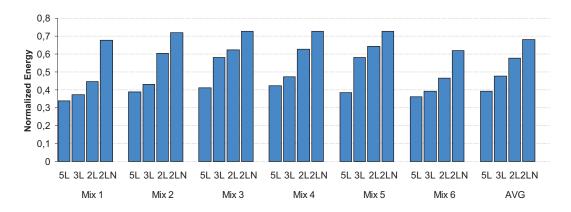

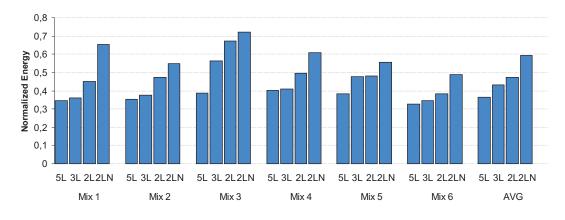

|   |     | 4.3.3 Energy Savings for HRT Mixes                               |   |   | <br>39         |

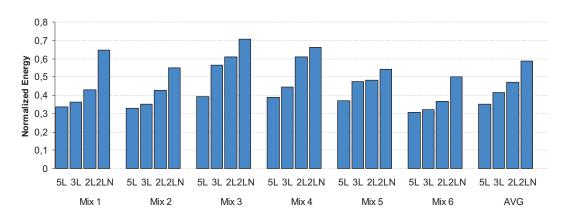

|   |     | 4.3.4 Energy Savings versus Deadline Misses for Hybrid Mixes     |   |   | <br>42         |

|   | 4.4 | Conclusions                                                      |   |   | <br>46         |

| 5 | Tas | k Migration                                                      |   |   | 47             |

|   | 5.1 | Introduction                                                     |   |   | <br>47         |

|   | 5.2 | Proposed Task Migration Heuristics                               |   |   | <br>47         |

|   |     | 5.2.1 Single Option Migration Policies                           |   |   | <br>48         |

|   |     | 5.2.2 Multiple Option Migration Dynamic Partitioner              |   |   |                |

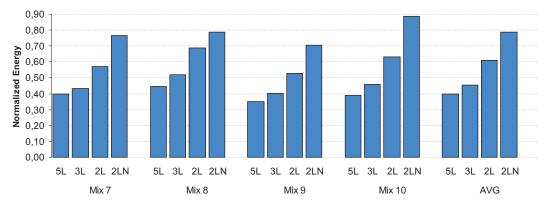

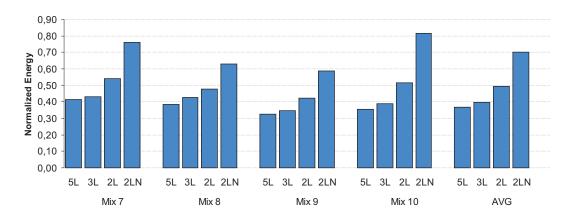

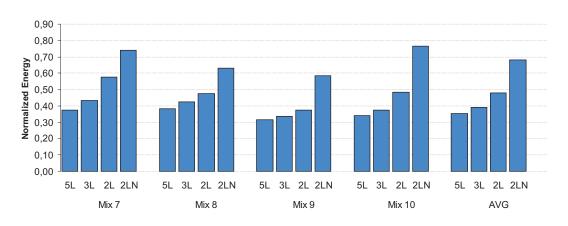

|   | 5.3 | Experimental Results                                             |   | • | <br>51         |

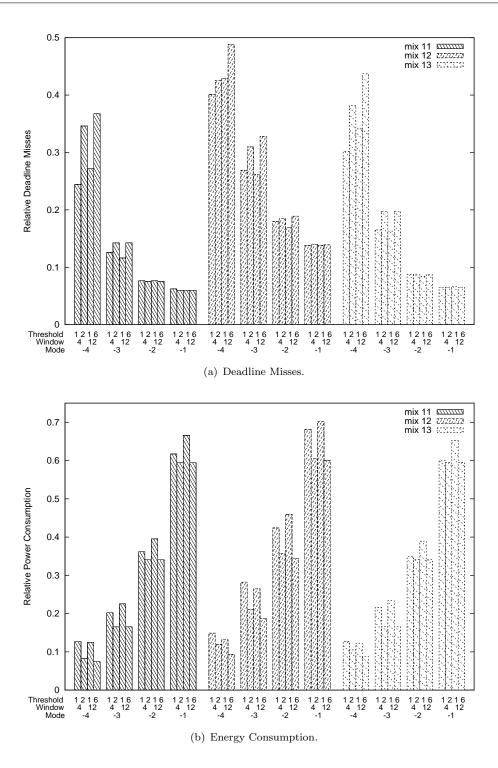

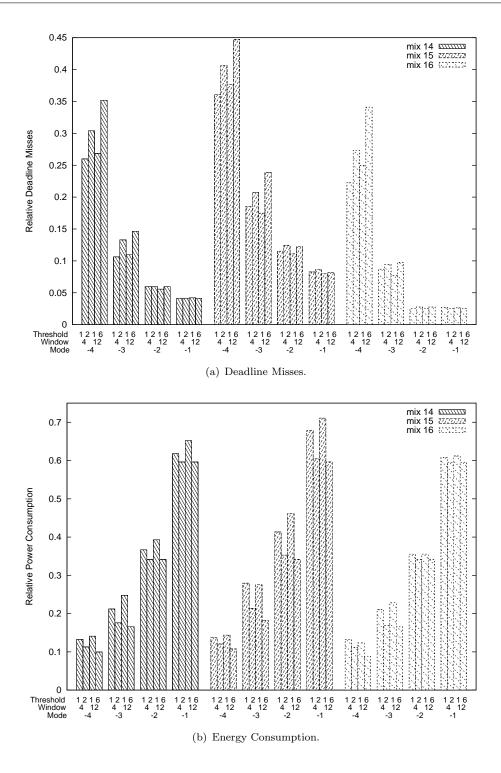

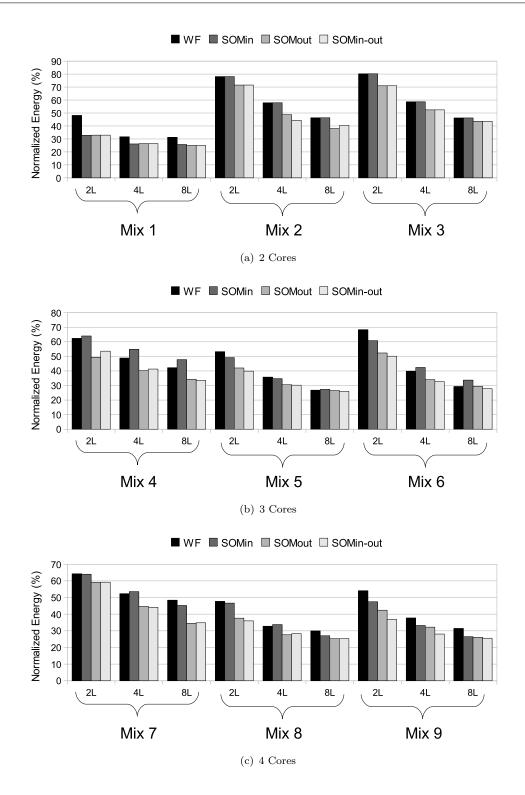

|   |     | 5.3.1 Impact of Applying Migrations at Specific Points of Time . |   |   | <br>53         |

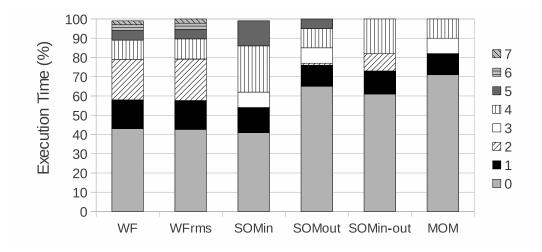

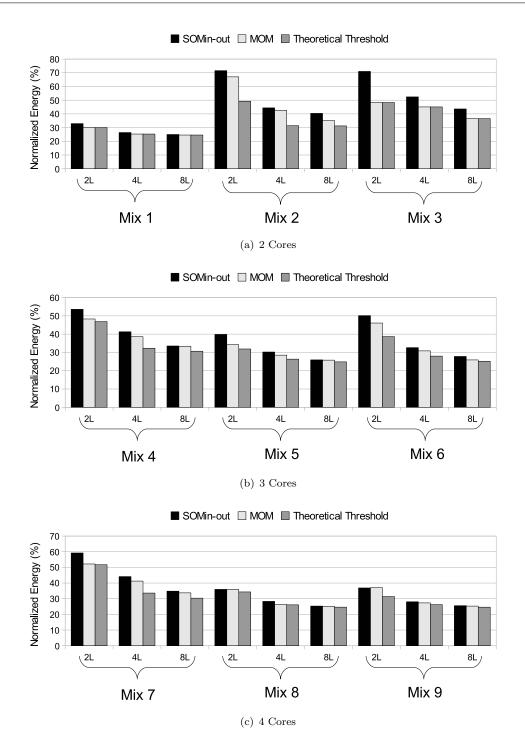

|   |     | 5.3.2 Comparing <i>MOM</i> versus <i>SOM</i> Variants            |   |   | <br>56         |

|   | 5.4 | Conclusions                                                      | ٠ | • | <br>59         |

| 6 |     | mory Controller Scheduling Policies                              |   |   | 61             |

|   | 6.1 | Introduction                                                     |   |   |                |

|   | 6.2 | Power-Aware Scheduler                                            |   |   |                |

|   | 6.3 | Memory Controller                                                |   |   |                |

|   |     | 6.3.1 HRT Requests First                                         |   |   |                |

|   |     | 6.3.2 Active Task Requests First                                 |   |   |                |

|   | 6.4 | Experimental Results                                             |   |   |                |

|   | 6.5 | Conclusions                                                      | • | • | <br>69         |

| 7 | •   | namic Execution Time Estimation                                  |   |   | 71             |

|   | 7.1 | Introduction                                                     |   |   |                |

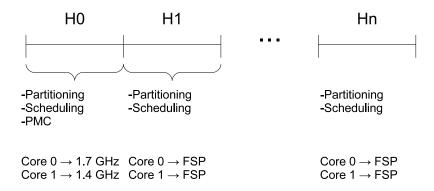

|   | 7.2 | System Architecture                                              |   |   |                |

|   |     | 7.2.1 Partitioning and Scheduling                                |   |   |                |

|   | 7.0 | 7.2.2 Memory System                                              |   |   |                |

|   | 7.3 | Processor-Memory Model                                           |   |   |                |

|   | 7.4 | Model Validation                                                 |   |   |                |

|   | 7.5 | Frequency Selection Policy based on the Proc-Mem Model           | • | • | <br>. 80<br>80 |

|   |     | A A L. ACHEUTHEL WOLKING DEHAVIOR                                |   |   | \d.            |

|    | 7.6   | 7.5.2 Experimental Results |    |

|----|-------|----------------------------|----|

| 8  | 8.1   | Contributions              |    |

| Re | efere | nces                       | 91 |

# List of Figures

| 1.1 | Components of the studied system and thesis contributions                                                                                   | 5  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Modeled system                                                                                                                              | 18 |

| 3.2 | Active and inactive periods example                                                                                                         | 23 |

| 3.3 | Decreasing and increasing frequency                                                                                                         | 26 |

| 4.1 | Load-bounded Resource Balancing heuristic. Legend: RES refers to the resource being balanced                                                | 31 |

| 4.2 | <u> </u>                                                                                                                                    | 33 |

| 4.3 |                                                                                                                                             | 34 |

| 4.4 | Example of the Gantt chart for mix 6. Continuous line means that the period is active. Discontinuous line means that the task is out of the |    |

| 4 = |                                                                                                                                             | 38 |

| 4.5 |                                                                                                                                             | 40 |

| 4.6 | 30 (                                                                                                                                        | 41 |

| 4.7 | 30 ( )                                                                                                                                      | 43 |

| 4.8 | Normalized deadline misses and energy (4 cores)                                                                                             | 44 |

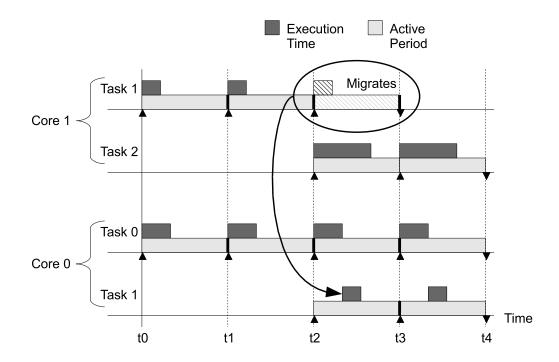

| 5.1 | Example of task migrations to balance the system workload                                                                                   | 49 |

| 5.2 | Migration Attempt algorithm                                                                                                                 | 50 |

| 5.3 | Multiple Option Migration dynamic partitioner algorithm                                                                                     | 51 |

| 5.4 | $SOM_{in-out}$ versus $MOM$ working example                                                                                                 | 52 |

| 5.5 | SOM variants comparison for different DVFS levels and number of cores.                                                                      | 54 |

| 5.6 | Effective action of the $SOM_{in}$ partitioning algorithm                                                                                   | 55 |

| 5.7 | Differences of the required frequencies in the 3-core system for mix 4                                                                      | 57 |

| 5.8 | $SOM_{in-out}$ versus $MOM$ for different DVFS levels and number of cores                                                                   | 58 |

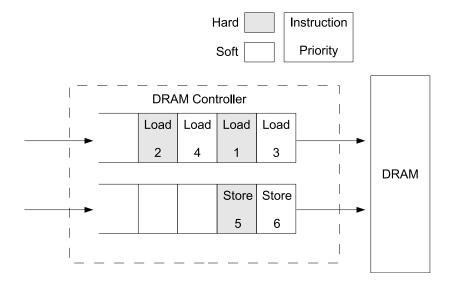

| 6.1 | HR-first request scheduling policy                                                                                                          | 64 |

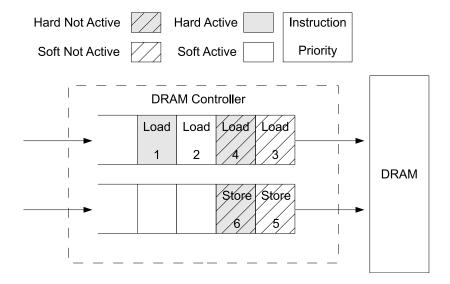

| 6.2 |                                                                                                                                             | 65 |

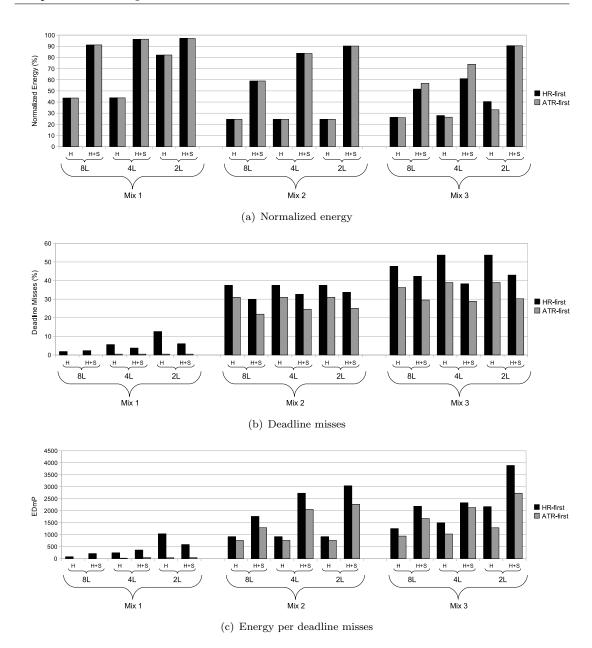

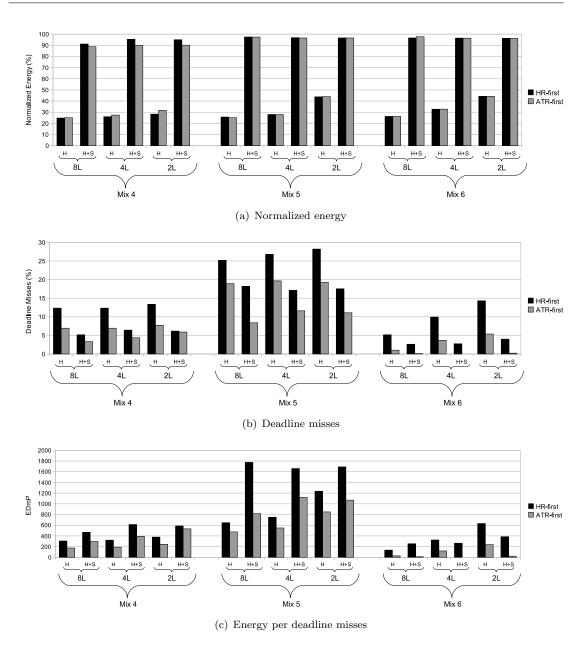

| 6.3 |                                                                                                                                             | 67 |

| 6.4 |                                                                                                                                             | 69 |

| 7.1 | System model                                                                                                                                | 72 |

| 7.2 | ·                                                                                                                                           | 74 |

| 7.3 | Execution overlap between processor and memory for two different fre-                                                                       |    |

| ,   |                                                                                                                                             | 75 |

| 7.4 | Estimates of the <i>Proc-Mem</i> model in stand-alone execution in the single-                                                              | 77 |

xviii List of Figures

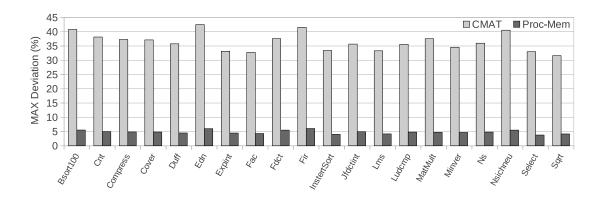

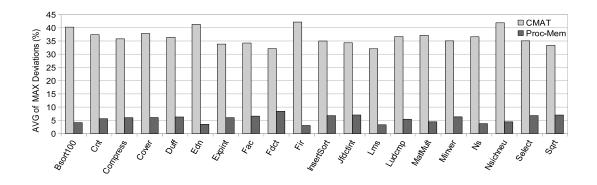

| 7.5 | Maximum deviation in processor cycles in a single-core superscalar archi-     |    |

|-----|-------------------------------------------------------------------------------|----|

|     | tecture.                                                                      | 78 |

| 7.6 | Average of maximum deviations in a multicore superscalar architecture         | 78 |

| 7.7 | Estimates of the <i>Proc-Mem</i> model in a multicore processor               | 79 |

| 7.8 | Power-aware scheduler actions of the system across the hyperperiods           | 80 |

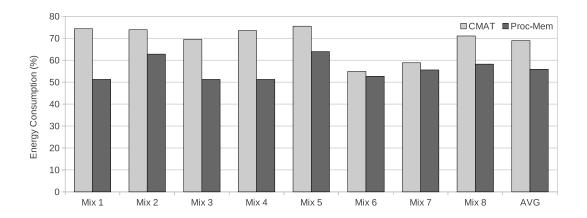

| 7.9 | Normalized energy consumption of <i>Proc-Mem</i> and <i>CMAT</i> with respect |    |

|     | to a system working at the maximum speed                                      | 82 |

# List of Tables

| 3.1 | Machine parameters                                                                                              | 19 |

|-----|-----------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Benchmark description                                                                                           | 20 |

| 3.3 | Frequency (F), voltage (V) and power (P) for each DVFS level                                                    | 21 |

| 4.1 | Benchmarks requirements and classification in categories H, M, L                                                | 35 |

| 4.2 | Benchmark mixes                                                                                                 | 36 |

| 4.3 | Benchmarks classification intervals attending to their processor requirements and memory reference instructions | 37 |

| 4.4 | Distribution of resource requirements and utilization (core 0, core 1) for each scheduling heuristic for mix 6  | 37 |

| 4.5 | QoS requirements trade-off                                                                                      | 45 |

| 5.1 | Benchmarks and mixes. Legend: * the benchmark appears more than once in the mix                                 | 53 |

| 5.2 | Algorithms action on workload changes                                                                           | 56 |

| 5.3 | Average and standard deviation of task utilization                                                              |    |

| 6.1 | Benchmarks and mixes. Legend: * the benchmark appears more than once in the mix                                 | 66 |

| 7.1 | Mix composition: benchmarks and instances of each benchmark                                                     | 81 |

| 7.2 | Deadline misses in the <i>CMAT</i> and <i>Proc-Mem</i> models and active periods of the mixes                   | 83 |

# Acronyms

ATR-first Active Task Requests first

BF Best Fit

CGMT Coarse-Grain MultiThreading

CMAT Constant Memory Access Time

DVFS Dynamic Voltage and Frequency Scaling

EDF Earliest Deadline First

FF First Fit

FSP Frequency Selection Policy

FGMT Fine-Grain MultiThreading

HRT Hard Real-Time

HR-first HRT Requests first

LRB Load-bounded Resource Balancing

MOM Multiple Option Migration

MPSoC MultiProcessor System-on-Chip

NRT Non Real-Time

OS Operating System

PDA Personal Digital Assistant

PMC Performance Monitoring Counter

Proc-Mem Processor-Memory

QoS Quality of Service

RMS Rate Monotonic Scheduling

SMP Symmetric Multiprocessor Platform

SMT Simultaneous MultiThreading

SOM Single Option Migration

SRT Soft Real-Time

xxii Acronyms

$\mathbf{WCET}$  Worst Case Execution Time

$\mathbf{WF}$  Worst  $\mathbf{F}$ it

$\mathbf{WRR}$  Weighted Round-Robin

## Chapter 1

# Introduction

#### 1.1 Motivation

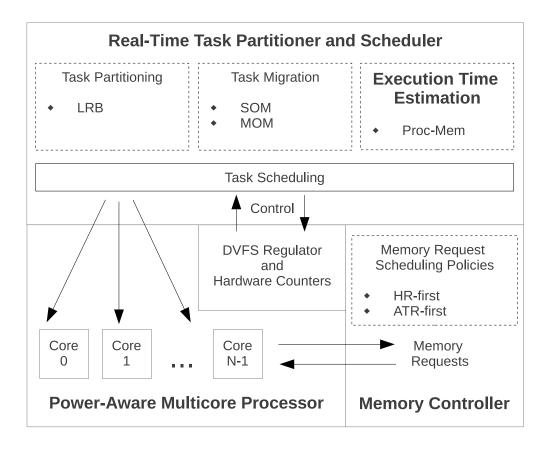

This chapter introduces the motivation and contributions of this thesis. The motivation deals with four main elements in a power-aware real-time multicore system: i) the power-aware multicore processor, ii) the real-time task partitioner and scheduler, iii) the memory controller, and iv) dynamic execution time estimation. These four elements are highlighted in bold letters in Figure 1.1. Next, we motivate the significance of these elements for the performance and power consumption of real-time systems.

#### 1.1.1 Power-Aware Multicore Processors

Because of technology advances power consumption has emerged up as an important design issue in modern microprocessors. This fact is especially critical when these processors are designed for real-time systems (e.g., robotics, sensor networks) and embedded systems (e.g., PDAs, mobile phones), where the battery lifetime is a crucial issue [1]. As a consequence, research on reducing power consumption has become a hot research topic when designing embedded computing systems [2–4].

A straightforward way to reduce power consumption consists on using processors that do not implement the most power-hungry microarchitectural mechanisms (e.g., the out-of-order issue logic). However, this situation does not always match the design constraints since processors must support a growing number of applications. Thus, many research

works have concentrated on attacking hot spots [5] or reducing consumption in the larger microprocessor components like the cache memory [6]. A different power management technique which applies on the whole microprocessor die and that is being implemented in most current microprocessors is *Dynamic Voltage and Frequency Scaling* (DVFS) [2]. It applies on the whole microprocessor and allows the system to improve its energy consumption by reducing the frequency when the processor has a low activity level (e.g., a mobile phone that is not being actively used). This technique allows the system to work at different frequency/voltage levels, and it has been implemented in many modern microprocessors like the Transmeta Crusoe [7], the Intel Xeon [8], or the Mobile AMD Duron [9].

Depending on either each core has its own DVFS regulator or the same regulator is used to supply voltage to all cores (forcing them to work at the same speed), DVFS can be classified as local and global, respectively. Local DVFS is more complex and expensive because more frequency/voltage regulators are required in the power delivery network. In this way, many multicore processors use a single clock domain since using independent clock domains is much more expensive, as stated in [1]. In addition, it has been shown that if the workload is properly balanced among the cores, global DVFS can be as efficient as local DVFS [10]. Thus, there are several high-performance processors, such as the IBM Power 7 [11], that implement global DVFS. However, recent manycore processors are incorporating multiple frequency/voltage domains, where each domain applies to a subset of the processor cores.

#### 1.1.2 Real-Time Task Partitioners and Schedulers

The problem of power aggravates with the increasing number of cores in the processors die [12], which is the current trend. In such processors, where different computational units are implemented, real-time systems include a workload partitioner in charge of distributing the task set among the available computational units according to a given heuristic [13, 14]. Typically, these heuristics only addressed the workload partitioning in the past; nevertheless, and due to energy concerns, power-aware heuristics have been recently proposed. In this context, several studies have analyzed the energy consumption by revisiting previous heuristics like the Worst Fit (WF) or Best Fit (FF) [15, 16].

Unfortunately, the nature of some workload mixes prevents the partitioner from achieving a good balance. To deal with this drawback some systems allow task migration in order to move their execution from one core to another, which results in energy saving improvements. Note that nowadays an *Operating System* (OS) is typically used to govern any embedded system (even in the form of a micro/pico kernel), however this study is abstracting the workload as a set of periodic tasks.

Regarding real-time constraints, the current embedded market requires these systems to host both Hard Real-Time (HRT) and Soft Real-Time (SRT) tasks, as well as tasks without timing constraints (i.e., Non Real-Time or NRT tasks). Unlike HRT environments where task deadlines must be guaranteed, in SRT environments this constraint is not mandatory, that is, deadline misses can be tolerated [17, 18]. Since in embedded systems HRT tasks are used to model critical applications due to safety and correctness reasons, SRT and NRT tasks are usually assigned the lowest priority. Nevertheless, a key requirement for market penetration of commodity embedded systems such as smartphones or tablets is to ensure not only a correct operation, but also the highest performance for SRT applications such as video streaming.

#### 1.1.3 Memory Controller Scheduling Policies

Besides, due to packaging restrictions, which are often accentuated in embedded systems, memory controllers are shared among a set of its computing cores. In this context, the cores sharing the same memory controller are said to belong to the same memory domain. Applications executing in the same memory domain may suffer contention when accessing the shared memory controller, which leads to unpredictable behavior. Thus, memory controller policies must be specially designed to tackle this issue.

To avoid unpredictable behavior in the execution of memory requests from critical applications, conventional memory controller scheduling policies used in NRT systems (e.g., FIFO) are not appropriate, since these policies can introduce a wide variability in the latencies of the memory requests, which is likely to cause HRT deadline misses. Recall that a deadline miss in HRT could lead to an important damage of the real-time system.

#### 1.1.4 Dynamic Execution Time Estimation

In addition, real-time systems require to estimate the Worst Case Execution Time (WCET) of the applications they run to ensure the system schedulability. The WCET must be estimated with the highest accuracy in order to provide either high Quality of Service (QoS) in SRT systems or to prevent possible damages due to deadline misses in HRT systems. Also, a high estimation accuracy allows the system to save power, improve the schedulability, or both.

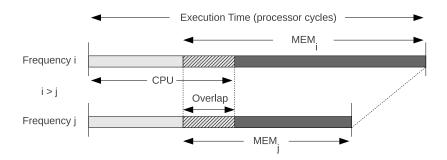

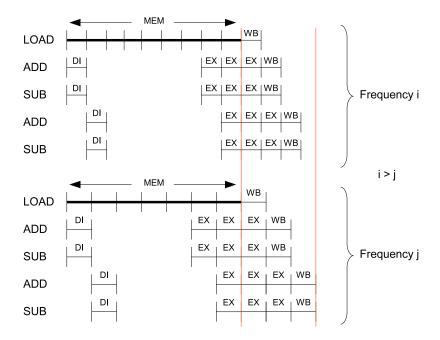

As commented above, there are severals aspects difficulting the estimation of the execution time of tasks in these processors. First, the running threads compete for shared resources such as the memory controller. Second, the aforementioned DVFS technique, aimed at managing power consumption more efficiently, difficults the execution time estimations, since it must be taken into account the range of frequencies that the regulator supports.

Typically, estimations of the WCET can be performed off-line by running the jobs in an isolated way. However, advances in processor design make this technique not appropriate for its use in most current multithreaded microprocessor generations. In addition, some research works assume that the memory access time (quantified in processor cycles) is constant regardless the processor frequency. This assumption considers that all the processor components scale their speed at the same pace. Nevertheless, it can bring important deviations to the estimation of the execution time since main memory devices have their own power supply and work independently of the processor DVFS regulator.

#### 1.2 Contributions of the Thesis

The goal of this thesis is to devise multiple techniques to reduce power consumption in a multicore embedded real-time system. This thesis offers four major contributions that are enclosed with dotted lines in Figure 1.1: i) task partitioning, ii) task migration, iii) memory request scheduling policies, and iv) dynamic execution time estimation. These contributions are described below:

#### 1. Task Partitioning.

A partitioning heuristic aimed at increasing the overlapping time between memory

FIGURE 1.1: Components of the studied system and thesis contributions

access and computation time is proposed. This algorithm distributes tasks, both HRT and SRT, among cores balancing the demand of a major system component (processor or memory) until a given utilization threshold is reached. Then, as all cores are assumed to work at the same speed (global DVFS), the less loaded core policy is followed to better balance speed requirements. In this context, there is a trade-off between the system frequency and the percentage of deadline misses. In other words, the lower the frequency, the less the energy consumption but also a higher number of deadline misses will rise and viceversa. The proposed algorithm, referred to as Load-bounded Resource Balancing (LRB), addresses this trade-off by varying the system speed, and uses a threshold as an indicator of acceptable deadline misses. To this end, different aggressiveness ways to increase and decrease the frequency have been devised. This technique varies the frequency to reduce power consumption while guaranteeing HRT deadlines and allowing the miss of some SRT deadlines.

#### 2. Task Migration.

Two algorithms allowing task migration are proposed. The simpler algorithm,

namely Single Option Migration (SOM), checks just one target core before performing a migration. In contrast, the Multiple Option Migration (MOM) searches the optimal target core. To address energy savings, the devised schedulers follow two main rules: (i) migrations are allowed only in those points of time when the workload changes, that is, when tasks enter or leave the system, and (ii) only one task is allowed to migrate each time because analyzing all the possible task migrations may result in a prohibitive overhead. Thes partitioner module is in charge of readjusting possible workload imbalances at run-time that may occur at arrivals or exits of tasks by applying task migration. To keep overhead low and to study the impact of the point of time when the algorithm is applied, three variants of the SOM algorithm have been devised, depending on the point of time the scheduler is applied: when a task arrives to the system  $(SOM_{in})$ , when a task leaves the system  $(SOM_{out})$ , and in both cases  $(SOM_{in-out})$ .

#### 3. Memory Controller Scheduling Policies.

A simple memory controller scheduling policy would prioritize requests of HRT tasks over the remaining ones, from now on *HR-first*. This would increase the number of deadline misses of SRT tasks and the execution time of NRT tasks, negatively impacting on the QoS of SRT and non-critical applications. Moreover, a high number of SRT deadline misses during HRT peak activity may leave the system unresponsive for significant periods of time. To overcome this problem, a novel memory controller policy, referred to as *ATR-first*, is proposed. This policy ensures *Earliest Deadline First* (EDF) schedulability without sacrificing QoS of non-critical applications. The proposed approach prioritizes only those requests of HRT tasks that are critical to accomplish real-time schedulability. For dynamic scheduling algorithms, such as EDF, this set of tasks varies during execution and depends on the running workload as well as the computing power of the system (i.e., number of cores and multithreading capabilities of each core).

#### 4. Dynamic Execution Time Estimation.

A model that dynamically predicts the execution time of real-time applications is proposed. The proposal, referred to as *Processor-Memory* (*Proc-Mem*), executes all the workload at the maximum speed during the first hyperperiod, which is used to collect the required inputs to the model. When this hyperperiod expires, the

model is used to estimate the lowest (i.e., the most energy-efficient) working frequency that fulfills the deadline through the different applications' periods. These input values are saved and used by the scheduler for subsequent hyperperiods. Notice that selecting the optimal frequency not only can bring important energy savings but also improves system schedulability. Besides, a Frequency Selection Policy (FSP) based on the model is also devised and compared with the Constant Memory Access Time (CMAT) model, where the memory access time (quantified in processor cycles) is constant regardless the processor frequency.

#### 1.3 Thesis Outline

This thesis is structured in 8 chapters. Chapter 2 discusses the related research. Chapter 3 describes the baseline system model and presents the simulation framework used for the experiments.. Chapter 4 introduces the *LRB* task partitioning algorithm. Chapter 5 explains both *SOM* and *MOM* task migration algorithms. Chapter 6 analyzes the proposed memory controller policies *HR-first* and *ATR-first*. Chapter 7 describes the *Proc-Mem* model to predict the execution time of real-time tasks. Finally, Chapter 8 summarizes the thesis and presents some concluding remarks.

## Chapter 2

# Related Work

This chapter presents the related work with the thesis contributions as described in Chapter 1.

# 2.1 Real-Time Scheduling in Power-Aware Multicore Processors

Numerous research papers have explored energy management on uniprocessor real-time systems. Most of them focus on periodic task systems [19, 20], but also some proposals have been published dealing with soft aperiodic tasks [21] and sporadic tasks [22]. Buttazzo et al. [19] present an algorithm for energy management based on DVFS that integrates the elastic scheduler for discrete voltage mode processors. In [20], AlEnawy et al. analyze the performance optimization problems for real-time systems that have to rely on a fixed energy budget during an operation. They adopt the weakly-hard real-time scheduling paradigm to ensure a predictable performance for all the tasks; that is, they minimize the number of dynamic failures (in terms of (m,k)-firm deadline constraints) while remaining within the energy budget.

To deal with both computational and power management requirements, many systems use multicore processors. These processors allow a more efficient power management than complex monolithic processors for a given performance level. In multiprocessors platforms, where energy efficient scheduling of real-time tasks is an NP-Hard problem [1, 15], two main scheduling categories exist depending on whether the task queue is

shared among all the processors (global scheduling) or not (partitioned scheduling). In the former case, tasks are allowed to migrate among processors and the highest priority executable tasks are selected for execution. For instance, in [23], Kato et al. present a global EDF based scheduler [24] for sporadic tasks. In the latter case, a task is assigned permanently to a given processor and it is not allowed to migrate. When using this technique the multiprocessor scheduling problem is split into several uniprocessor scheduling problems. Therefore, well established algorithms such as EDF and RMS (Rate Monotonic Scheduling) from uniprocessor theory can been adopted. For example, in [16], AlEnawy et al. consider the problem of energy minimization for periodic preemptive HRT tasks scheduled on a Symmetric Multiprocessor Platform (SMP) with DVFS capability. In [25] Zikos et al. present an energy aware algorithm for clusters of heterogeneous processors, based on favoring job allocation to the most energy efficient processors. Notice that these works do not model multithreaded processors, which are standard nowadays.

Many manufacturers (e.g., Intel, IBM, Sun, etc.) deliver processors providing multithreading capabilities, that is, they provide support to run several threads simultaneously. Some examples of current multithreaded processors are Intel Montecito [26] and

IBM Power 5 [27]. Also, leading manufacturers of the embedded sector, like ARM,

plan to include multithreading technology in next-generation processors [28]. Regarding research in these multithreaded systems, in [29], Park et al. provide a performance

guaranteed energy management for multithreaded applications in multicore processors.

In [30] Cazorla et al. present an architecture where a Simultaneous MultiThreading

(SMT) processor interacts with the OS to improve real-time predictability. However,

none of these works consider real-time schedulability and energy management as a whole.

In [31], El-Haj-Mahmoud et al. state that SMT processors hardly provide HRT guarantees, and proposes virtualizing them into multiple single-threaded superscalar processors.

This architecture incorporates a static scheduler to execute periodic tasks. They compare their scheduler to a multiprocessor implementing EDF in terms of rate of deadline

misses. Nevertheless, this work does not tackle energy consumption.

#### 2.1.1 Task Partitioning

With respect to partitioning heuristics, many proposals have recently been published. In [32] Wei et al. exploit parallelism of multimedia tasks on a multicore platform combining DVFS with switching-off cores to reduce energy consumption. In [15], Aydin et al. develop a framework where load balancing is used to produce energy-efficient partitionings of real-time tasks in a SMP system with DVFS. These partitionings are evaluated using the EDF algorithm. Schranzhofer et al. [33] presented a method for allocating tasks to cores in a multiprocessor platform, aimed at minimizing the average power consumption, however, the application is modeled without considering timing constraints. In [16], authors focus on the impact of heuristics on feasibility and energy consumption, and propose a new one that reserves a subset of processors for light tasks. In [34] Brandenburg et al. present an empirical evaluation of several global and partitioned scheduling algorithms. The evaluation was conducted on a Sun Niagara multicore platform with 32 logical CPUs (eight cores and four hardware threads per core). Although each tested algorithm proved to be a feasible choice for some subset of the considered workload categories, they do not take into account power saving aspects. Finally, concerning memory-processor overlapping, El-Haj-Mahmoud et al. [35] devise a technique for tolerating memory latencies in HRT systems implemented in Coarse-Grain MultiThreading (CGMT) processors. They derive a closed-form schedulability test to determine whether a HRT task set is schedulable in the context of Weighted Round-Robin (WRR) scheduling on a multithreaded processor. Unfortunately, this work does not deal with energy management and multiple cores.

#### 2.1.2 Task Migration

Some proposals dealing with task migration can be found in the bibliography. Brandenburg et al. [34] evaluate global and partitioned scheduling algorithms in terms of scalability, although power consumption was not investigated. In [36], Zheng divides tasks into fixed and migration tasks, allocating each of the latter category to two cores, so they can migrate from one to another. Unlike this thesis, that paper does not consider dynamic workload changes, instead, all tasks are assumed to reach the system at the same instant, so migrations can be scheduled off-line. In [37] Brião et al. analyze how migrating SRT tasks affects NoC-based MPSoCs in terms of deadline misses and

energy consumption for non-threaded architectures. See et al. [1] present a dynamic repartitioning algorithm with migration to balance the workload and reduce power consumption. They perform a theoretical exploration assuming parameters like number of cores and number of tasks, but neither computational core nor real-time benchmarks are used through their evaluation. Thus, their main contribution is the theoretical estimation of benefits. Fisher and Baruah [38] derived near-optimal sufficient tests for determining whether a given collection of jobs with precedence constraints can feasibly meet all deadlines upon a specified multiprocessor platform allowing task migration under global EDF scheduling. However, this work does not tackle reduction of energy consumption, which is major concern of this research. Notice that in multicores, task migration may cause additional traffic for the coherence protocol too; this problem has been studied previously and reduced by modification to the coherence scheme [39].

#### 2.2 Memory Controller Scheduling Policies

Schliecker et al. [40] and Pellizzoni et al. [41] analyze the delay of memory access in systems where several simultaneously-running tasks share the main memory. Their proposals require a detailed profiling of application memory access patterns and a deep understanding of the memory scheduling policy.

Predator [42] is a memory controller for multiprocessors that guarantees a bandwidth requirement to a given task and requires the user to assign a fixed priority to each task. The controller is implemented in the network interface of a network on chip targeted for a specific DRAM device, a JEDEC-compliant 32 Mb 16 DDR2-400B SDRAM. This solution fits well in streaming or multimedia real-time applications, in which a bandwidth QoS requirement can be easily defined.

In [43], Paolieri et al. present a JEDEC-compliant DDRx SDRAM analyzable memory controller for multicore architectures that reduces the impact that a memory request can suffer due to the memory interferences introduced by other tasks, allowing the computation of tight WCET estimations. This research is orthogonal to the memory controller scheduling policy proposed on this thesis, that improves QoS of SRT tasks in a heavily loaded real-time system.

In [44], a shared memory multicore that allows concurrent execution of HRT and non-HRT applications is proposed. They give an Upper Bound Delay to memory requests of HRT tasks, so that these tasks can meet their deadlines while providing high-performance for non-HRT tasks. However, the power consumption of the proposal is not tackled. To the best of our knowledge, our work addresses for the first time the trade-off between the energy consumption and SRT QoS while guaranteeing HRT constraints.

#### 2.3 Execution Time Estimation

A number of static WCET analysis methods have been designed in the last two decades, mainly for monoprocessors [45]. These research works use execution time estimates to choose the optimal DVFS level to enhance power savings and reduce deadline misses. Seth et al. [46] study the effects of DVFS on static timing analysis taking into account power consumption. They calculate the execution time in any frequency range using a parametric model that depends on the number of cache misses. However, their approach is static and needs the source files of the applications. Another model is proposed by Snowdon et al. [47]. They perform an on-line evaluation of application characteristics using performance counters, nevertheless, it is combined with an off-line characterization of the hardware platform. Miftakhutdinov et al [48] propose a DVFS performance predictor for memory systems with a streaming prefetcher. They also take into account that memory latencies (as measured in seconds) are not affected by frequency scaling. However, their proposal is static, without real-time constraints and does not consider multiple cores. Unlike these works, our proposal dynamically estimates the execution time and focuses on multicore processors.

Some work has dealt with the estimation of the execution time of concurrent tasks. Several studies focus on timing analysis for single-threaded architectures by using static code analysis. Schaefer et al. [49] propose to measure execution time at basic block level and using this data to estimate WCET of the entire program. Wenzel et al. [50] propose a decomposition of the program into segments performing a timing analysis for each segment. Authors also propose an approach for program segmentation that balances the number of program segments with the average number of paths per segment. These studies propose improvements of measurement-based timing techniques for single-threaded processors.

Regarding multithreading, Cullmann et al. [51] analyze the design of future multithreaded processors for time-critical systems. They show that some processor designs make the timing analysis infeasible and suggest design principles for making multithreaded architectures predictable. Based on the theoretical analysis, authors give guidelines for designing predictable architectures.

Finally, in [52], Radojković et al. propose a method that quantifies the slowdown that concurrent tasks may experience due to contention in shared processor resources. The presented method is used to determine if a given multithreaded processor is a good candidate for systems with timing requirements. They use the method to analyze three multithreaded architectures exhibiting different configurations of resource sharing. However, they do not tackle the schedulability analysis of the system.

Execution time estimation for multicore platforms has been the subject of rather few studies. Most of them focused on cache-aware methods. Hardy et al. [53] present a WCET estimation method for multicore platforms with shared instruction caches. The proposed method provides estimates through the control of the contents of the shared instruction caches. More precisely, by caching only the blocks statically known to be reused and bypassing from shared caches the other blocks.

There are some works that study the effect of the main memory in the estimation of the WCET for multithreaded and multicore architectures. Shah et al. [54] make use of bank interleaving and applying *Priority based Budget Scheduling* (PBS) to share SDRAM among multiple masters. This technique permits to bound the WCET of an application accessing a shared SDRAM using the worst case access pattern. They implemented the memory system in an FPGA. Their proposal produces safe and low WCET bounds. Ungerer et al. [55] build a predictable multicore architecture for mixed critical applications. Predictability is achieved by giving the highest priority to the HRT tasks while on the shared bus access latency is bounded by a *Round Robin* (RR) scheduling policy. The memory is accessed through an *Analyzable Memory Controller* (AMC), which implements bank interleaving. Through theoretical analysis, latency parameters are extracted to calculate the WCET. The AMC applies the maximum of Read/Write and Write/Read switching latencies as a constant worst case latency on every access. Such assumption, while making the analysis simple, cannot produce precise bounds. Moreover, the RR policy with one request per master cannot satisfy the need

of different bandwidth requirements. If more than one request per master is assigned, the WCET is severely degraded [54].

## Chapter 3

# System Model

This chapter presents the baseline multicore system used in this thesis. We also detail the extensions that have been carried out to the Multi2Sim [56] simulation framework to model real-time constraints.

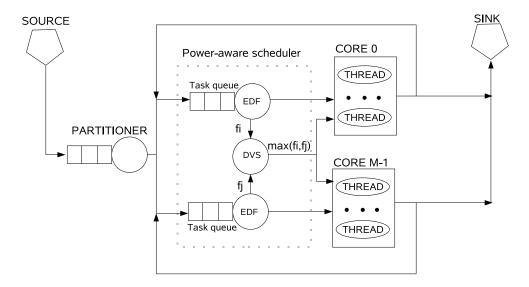

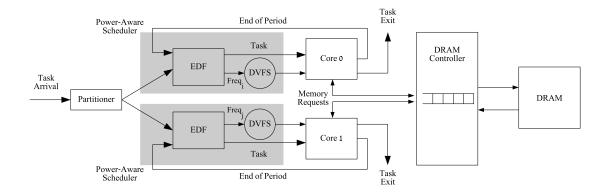

## 3.1 Baseline Design

The multicore system studied in this thesis consists of a source and a sink of real-time tasks, a workload partitioner, a power-aware scheduler, and a multicore processor with m cores. Figure 3.1 depics a block diagram of the modeled system.

When a task arrives to the system, a partitioner module allocates it into a task queue associated to a given core, which contains the tasks that are ready for execution in that core. These queues are components of the power-aware scheduler that controls a global DVFS regulator [2]. In this scheme, the scheduler is in charge of adjusting the working frequency of the cores in order to satisfy the workload requirements.

The system consists of multiple superscalar cores that can issue more than one instruction to execution every cycle. Besides, due to energy constraints of embedded systems, an in-order issue logic has been assumed, as deployed in embedded processors like the Intel Atom [57]. Table 3.1 summarizes the simulated machine architectural parameters of each core.

Figure 3.1: Modeled system.

Many commercial systems are implementing multithreading capabilities in multicore processors. To this end, three main paradigms can be used: Simultaneous Multi-Threading (SMT), Coarse-Grain MultiThreading (CGMT) and Fine-Grain MultiThreading (FGMT) [58]. For instance, Intel's Montecito [26] multicore processor implements CGMT while Sun's UltraSPARC T2 [59] uses FGMT. Several SMT implementations also exist in commercial processors, like the IBM Power 5 [27] or the Intel Atom [60].

SMT processors are more complex and less predictable. Because of these reasons, this work focuses on CGMT which offers a good trade-off between power consumption and real-time schedulability [35]. CGMT processors provide multithreading capabilities by switching the running thread when a long latency event occurs (e.g., a memory access). In such a case, a new thread takes the processor control while the other performs the memory access, so during the long latency event both threads are allowed to overlap their execution. In this context, the saved time can be devoted to reduce frequency in order to save energy. If the new thread also stalls due to a long latency memory event, then the issue slots are temporarily reassigned to the highest priority thread among those that are not waiting for memory, until the event is resolved. This thread switch can occur among the available hardware threads. That is, the issue slots are always assigned to the hardware thread executing the task with the highest real-time priority, which varies according to the scheduling algorithm.

| Microprocessor core  |                             |  |  |

|----------------------|-----------------------------|--|--|

| Issue policy         | In order                    |  |  |

| Fetch kind           | Switch on event             |  |  |

| Branch Prediction    | Two-level global history    |  |  |

|                      | 256 entries BTB, 4096 2-bit |  |  |

|                      | saturating counters GHB     |  |  |

| Issue bandwidth      | 2 instructions/cycle        |  |  |

| # Int ALUs, mult/div | 2,1                         |  |  |

| # FP ALUs, mult/div  | 2,1                         |  |  |

Table 3.1: Machine parameters.

### 3.1.1 Real-Time Tasks

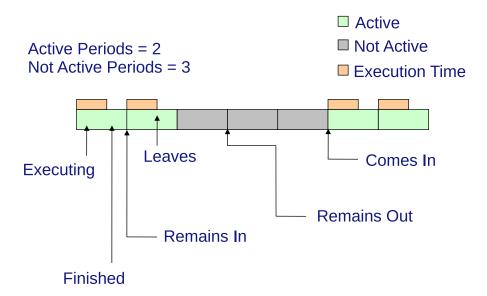

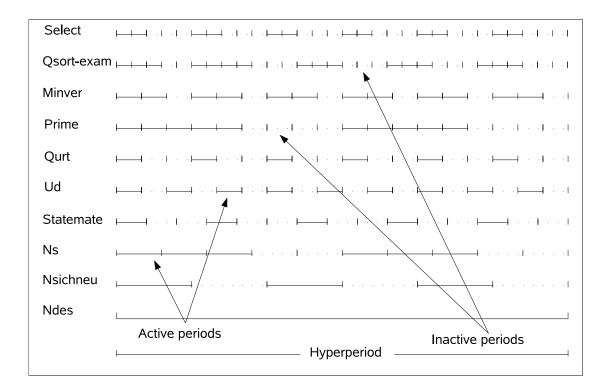

The system workload executes periodic real-time tasks. There is no task dependency and each task has its own period of computation. A task can be launched to execute at the beginning of each active period and it must end its execution before reaching its deadline. The end of the period and the deadline of a task are assumed to be the same for a more tractable scheduling process. There are also some periods where tasks do not execute since they are not active (i.e., inactive periods). In short, a task arrives to the system, executes during several active periods repeatedly, leaves the system, remains out of the system for some inactive periods, and then it enters the system again. This sequence of consecutive active and inactive periods allows modeling real systems with mode changes. Table 3.2 shows the benchmarks from WCET Analysis Project [61] that have been used to prepare real-time workload mixes.

Besides its period and deadline, a task is also characterized by its WCET. The WCET is obtained by executing the task in isolation. To avoid WCET variability due to concurrent execution, we assume that the processor and the memory controller support priorities.

The task utilization is obtained as  $U = \frac{WCET}{Period}$  and it is used by several schedulers and partitioners to check whether schedulability of the task set is feasible or not.

#### 3.1.2 Power-Aware Scheduler

The power-aware scheduler is composed of an EDF scheduler per core and the global DVFS regulator [10]. Once a task is allocated to a core, it is inserted into the task queue of that core. These queues are ordered according to the EDF policy, which prioritizes

| NT                   | E ' D ' '                                     |

|----------------------|-----------------------------------------------|

| Name                 | Function Description                          |

| Adpcm                | Adaptive pulse code modulation algorithm      |

| Bitcnts              | Test program for bit counting functions       |

| Bs                   | Binary search for a 15-element array          |

| Bsort100             | Bubblesort program                            |

| Cnt                  | Counts non-negative numbers in a matrix       |

| Compress             | Data compression program                      |

| Cover                | Program for testing many paths                |

| $\operatorname{Crc}$ | Cyclic redundancy check on 40-byte data       |

| Duff                 | Copy 43-byte array                            |

| Edn                  | FIR filter calculations                       |

| Expint               | Series expansion for integral function        |

| Fac                  | Factorial of a number                         |

| Fdct                 | Fast Discrete Cosine Transform                |

| Fft1                 | 1024-point Fast Fourier Transform             |

| Fibcall              | Simple iterative Fibonacci calculation        |

| Fir                  | Finite impulse response filter                |

| Insertsort           | Insertion sort on a reversed array of size 10 |

| Janne_complex        | Nested loop program                           |

| Jfdctint             | Discrete-cosine transformation                |

| Lcdnum               | Read ten values, output half to LCD           |

| Lms                  | LMS adaptive signal enhancement               |

| Loop3                | Function with diverse loops                   |

| Ludcmp               | LU decomposition algorithm                    |

| Matmult              | Matrix multiplication of two 20x20 matrices   |

| Minmax               | Minimum and maximum functions                 |

| Minver               | Inversion of floating point matrix            |

| Ndes                 | Complex embedded code                         |

| Ns                   | Search in a multi-dimensional array           |

| Nsichneu             | Simulate an extended Petri Net                |

| Prime                | Calculates whether numbers are prime          |

| Qsort-exam           | Non-recursive version of quick sort algorithm |

| Qurt                 | Root computation of quadratic equations       |

| Select               | Nth largest number in a floating point array  |

| Sqrt                 | Square root function                          |

| Statemate            | Automatically generated code                  |

| Ud                   | Calculation of matrixes                       |

Table 3.2: Benchmark description.

the tasks whose deadlines expire earlier. Thus, the tasks with the closest deadlines will be the ones mapped into the hardware threads implemented in each core. If some thread context is occupied by a lower priority task, preemption is applied.

Once the control logic of the global DVFS receives the speed requirements from all the EDF schedulers in the system, it supplies to the cores an appropriate frequency/voltage level to fulfill these requirements. The target frequencies are recalculated only when

| F[MHz]   | 1700 | 1500 | 1400 | 1300 | 1200 | 1100 | 900 | 600  |

|----------|------|------|------|------|------|------|-----|------|

| V[Volts] | 1.48 | 1.48 | 1.48 | 1.39 | 1.18 | 1.18 | 1   | 0.96 |

| P[Watts] | 24.5 | 24.5 | 22   | 22   | 12   | 12   | 7   | 6    |

TABLE 3.3: Frequency (F), voltage (V) and power (P) for each DVFS level.

the workload changes, that is, when a task arrives to and/or leaves the system. In the former case, a higher speed can be required because the workload increases. In the latter, it could happen that a lower frequency could satisfy the deadline requirements of the remaining tasks.

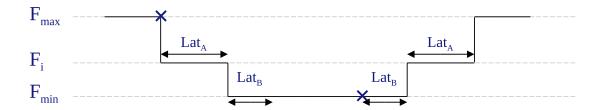

Table 3.3 shows the different frequency/voltage values considered for the power-aware scheduler based on the frequency levels of a Pentium M [62]. Frequency changes are not considered instantaneous since some time is needed to overcome the voltage gap between two different DVFS levels. In this sense, the latency of changing the DVFS level has been modeled according to a voltage transition rate of  $1mv/1\mu s$  [63]. To model this latency and the power overhead caused by these changes, the worst case for that transition has been assumed. That is, during a frequency transition the speed of the lowest frequency and the power consumption of the highest one are considered.

To calculate the energy consumption, the number of cycles working at each frequency is multiplied by the energy required per cycle at that frequency. Then, this value is normalized using as baseline the energy consumed by the system working always at the maximum speed. Notice that it is important to reduce the time spent at the higher frequency/voltage levels, since the normalized power for a given technology (e.g., 45nm) grows exponentially with the processor clock [1]. Thus, the scheduler must concentrate on the most efficient frequency/voltage levels.

## 3.2 The Multi2Sim Simulation Framework

Multi2Sim [56] is a cycle-by-cycle execution driven simulation framework for evaluating processors, which is being used by manufacturer companies like AMD or NVIDIA. As in commercial processors, three main parts can be distinguished: the core, the cache hierarchy and the interconnection network. Multithreaded cores can be modeled on this simulator with three multithreading paradigms: FGMT, CGMT and SMT. Distinct

configurations are allowed to represent different sharing strategies of pipeline stages and resources. It models different memory hierarchies with diverse sharing strategies and cache levels among cores and threads. A cache coherence protocol (MOESI) for sharing data among cores is also implemented. Finally, several interconnection network topologies can be configured.

#### 3.2.1 Simulation Models

In Multi2Sim three different simulation techniques are used: Functional Simulation, Detailed Simulation and Event-Driven Simulation (timing simulation is performed by the latter two). Functional Simulation is implemented as an autonomous module that provides an interface to the rest of the simulator. It does not consider any hardware structure, as cores or threads, it just deals with software contexts. Its main functions are to create and destroy contexts, perform program loading, enumerate existing contexts and consult their status, execute machine instructions and handle speculative execution. In Detailed Simulation the specific hardware microarchitecture is taken into account, with elements as pipeline structures (stage resources, instruction queues, reorder buffer, etc), branch predictor, cache memories or segmented functional units. Each cycle the detailed simulation module uses the functional simulation module interface to update the context status. The Detailed Simulation module analyzes the recently executed instructions accounting the operation latencies caused by hardware structures. With functional and detailed simulation built in independent modules, the implementation of machine instructions behaviour can be centralized in a single file (functional simulation), while function calls that activate hardware components (detailed simulation) return the latency required to be completed. In some situations that latency cannot be calculated when the function is called, it needs to be simulated cycle by cycle. That is the case of the interconnection network and cache memories. In that situation an Event-Driven Simulation module is required to obtain delays of message transfers caused by memory accesses.

#### 3.2.2 Main Proposed Extensions

In order to make Multi2Sim able to support real-time tasks and, at the same time, model a power-aware system, many extensions have been implemented in an additional

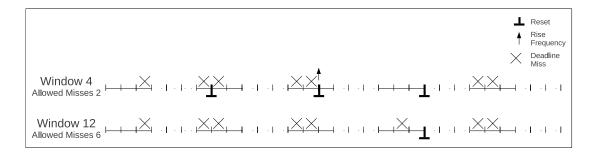

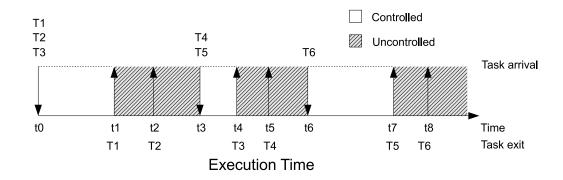

FIGURE 3.2: Active and inactive periods example.